# ORGANISATION EUROPEENNE POUR LA RECHERCHE NUCLEAIRE EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH

Laboratoire Européen pour la Physique des Particules European Laboratory for Particle Physics

# THE K-CHIP REFERENCE MANUAL

# **DRAFT**

V3A.2

Author: Kloukinas Kostas, CERN EP/CME

Version: 3A.2

Date: November 10, 2001

Last Update: January 22, 2004

Notes: This document describes the "Kchip\_V3" version of the Kchip.

This is a draft version of the K-chip reference manual.

## **Document History**

**Version 0.1 DRAFT**: this is the first draft of the K-chip reference manual. All included information should be considered as *target specifications*.

Version 0.2 DRAFT: this version of the manual includes the design changes on the chip in order to interface with the PACE3 chip and the AD41240 0.25µm ADC. All included information should be considered as *target specifications*.

**Version 0.3 DRAFT**: this version of the manual is an update of the previous version. All included information should still be considered as *target specifications*.

**Version 3A.1**: this version of the manual is an update of the previous version. Corrections: a) the width of the Bunch Counter is 12-bit and not 16-bit on page 7 and b) reassignment of the Trigger Commands in Table2-1 on page10. This manual reflects the functionality implemented in "**Kchip\_V3**" version of the Kchip. This version of the chip will be replaced by "**Kchip\_V3**b".

**Version 3A.2**: Updated information concerning the internal registers of the chip.

## **Design Team**

Kloukinas Kostas, EP/CME, e-mail: <u>Kostas.Kloukinas@cern.ch</u> Bonacini Sandro, EP/MIC, e-mail: <u>Sandro.Bonacini@cern.ch</u>

# **Table Of contents**

| 1 | Intro                                | ductionduction                                                                                          | 4                 |

|---|--------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|

|   | 1.1 P                                | reshower Front End System                                                                               | 4                 |

| 2 | The K                                | ζ-chip                                                                                                  | 5                 |

|   | 2.1 F<br>2.1.1<br>2.1.2              | Unctional Description                                                                                   | 5                 |

|   | 2.2 B                                | lock Diagram                                                                                            | 6                 |

|   | 2.3                                  | peration Modes                                                                                          | 8                 |

|   | 2.4 P                                | ACE Interface                                                                                           | 9                 |

|   | 2.5 A                                | DC interface                                                                                            | 9                 |

|   | 2.6 T                                | rigger Decoder                                                                                          | 10                |

|   |                                      | E-chip Buffers  Buffer Sizes  Data FIFO  Column Address FIFO  Trigger FIFO                              | .11<br>.12<br>.13 |

|   | 2.8 P                                | ACE supervisor                                                                                          | 14                |

|   | 2.9 K                                | Cchip Data Path design                                                                                  | 15                |

|   | 2.10<br>2.10.1<br>2.10.2             | Error Conditions / Error handling  Buffer Overflows  Synchronization of PACE3 chips                     | .16               |

|   | <b>2.11</b> 2.11.1                   | Packet Formatter                                                                                        |                   |

|   | 2.12.1<br>2.12.2<br>2.12.3<br>2.12.4 | Gigabit Link Interface  Physical Layer  Link Layer  Using CIMT protocol  Using 8b/10b encoding protocol | .19<br>.21<br>.22 |

|   | <b>2.13</b> 2.13.1                   | Link Synchronization Issues  Link Test Mode                                                             |                   |

|   | <b>2.14</b> 2.14.1 2.14.2            | Calibration Circuit  The DLL circuit                                                                    | .25<br>.25        |

|   | 2.15                                 | I <sup>2</sup> C Interface                                                                              | 25                |

| 3 | <b>SEU</b>                           | Tolerant Techniques                                                                                     | 27                |

|   | 3.1 G                                | eneral Architecture                                                                                     | 27                |

|   | 3.2 S                                | tate Machines                                                                                           | 27                |

|   | 3.3 C                                | onfiguration Registers                                                                                  | 29                |

|    | 3.4 Th           | ne SEU_COUNTER                                     | 29 |

|----|------------------|----------------------------------------------------|----|

| 4  | Intern           | al Registers                                       | 31 |

|    | 4.1.1            | The CONFIG Register                                |    |

|    | 4.1.2            | The ECONFIG Register                               | 33 |

|    | 4.1.3            | The STATUS_0 Register                              | 34 |

|    | 4.1.4            | The STATUS_1 Register                              |    |

|    | 4.1.5            | The FIFOMAP Register                               |    |

|    | 4.1.6            | The FIFODATA Register                              |    |

|    | 4.1.7            | The EVNCNT Register                                |    |

|    | 4.1.8            | The BNCHCNT Register                               |    |

|    | 4.1.9            | The MASK_T1CMD Register                            |    |

|    | 4.1.10           | The LAST_T1CMD Register                            |    |

|    | 4.1.11           | The KID Register                                   |    |

|    | 4.1.12           | The LATENCY Register                               |    |

|    | 4.1.13           | The GINT_BUSY Register                             |    |

|    | 4.1.14<br>4.1.15 | The GINT_IDLE register The CalPulse_DELAY register |    |

|    | 4.1.15           | The CalPulse_WIDTH register                        |    |

|    | 4.1.17           | The ADC_LATENCY register                           |    |

|    | 4.1.17           | The PFIFO_Overflow register                        |    |

|    |                  | · -                                                |    |

|    |                  | vent reading/writing through I2C                   |    |

|    | 4.2.1            | Event writing through I2C                          |    |

|    | 4.2.2            | Event reading through I2C                          |    |

| 5  | Opera            | ting Conditions                                    | 41 |

|    | 5.1 Re           | ecommended Operating Conditions                    | 41 |

| 6  | Timin            | g Characteristics                                  | 41 |

|    |                  | ging                                               |    |

| 7  |                  |                                                    |    |

| 8  | Pin As           | ssignments                                         | 43 |

| 9  | Appen            | dixes                                              | 47 |

|    | 9.1 Ko           | chip Interfacing                                   | 47 |

|    |                  | •                                                  |    |

|    |                  | ACE3 Overflow Probability simulation results       |    |

|    |                  | ACE3-AM DLL                                        |    |

|    | 9.4 K            | chip Design Review minutes Date: 4/4/2002          | 52 |

| 11 | ) Refe           | erence Documents                                   | 56 |

## 1 Introduction

This document describes the architecture and the implementation of the K-chip ASIC.

## 1.1 Preshower Front End System

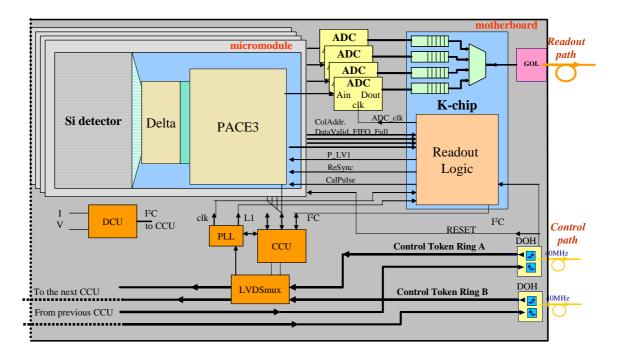

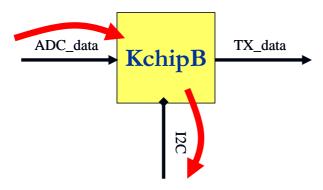

Figure 1-1 The general system architecture of the Preshower Front End Readout electronics.

## 2 The K-chip

## 2.1 Functional Description

The K-chip serves two functions:

- Data Merging from four PACE chips and

- PACE Readout Control

#### 2.1.1 Data Merging

As a Data Merger the K-chip function is to gather data from four PACE chips and format it in a way suitable to be sent over the high-speed digital link. As no data reduction occurs in the front-end system, the K-chip has to cope with the data rates produced by the PACE front-ends; this is detailed in the following sections.

The K-chip receives data in parallel from the PACE chips, builds a packet in a format suitable for the high-speed serial link and sends this to the remote FED cards.

While preparing this data block the K-chip adds some more information to it such as:

- an event number tag

- a bunch counter tag

- CRC information

- error information, if necessary

As the input data comes in 12 bit format, the K-chip aligns the data in contiguous blocks of 16 bits as to maximally utilize the link bandwidth. The data analysis engine in the FED cards will have to unpack the data into 12 bit wide words.

The dataflow used is a simple push type architecture. All K-chips in the system are synchronous and transmit data along their link at the same time, as no data reduction is performed until the FEDs level. Event data prepared in the K-chip buffers are sent to the serial link transmitter. To simplify the system and reduce its cost this link is unidirectional and without flow-control. This means that whenever an error occurs in the transmission medium (either the serializer, the link itself or the receiver) a block of data belonging to one (or potentially even more) event(s) is irremediably lost. As another consequence, the FED has to be able to regain synchronization when one of the K-chips or links is sending data under some error condition.

#### 2.1.2 PACE Readout Control

The K-chip generates the fast timing signals for the PACE operation. These signals are:

- the 40MHz system clock,

- the PACE 1<sup>st</sup> Level Trigger pulse (P\_LV1),

- the FE readout Synchronization pulse (ReSync), and

- the Calibration Pulse (CalPulse).

The K-chip supervises the readout operation of the PACE chips that are connected to its four channel ports by monitoring the following PACE signals:

- The PACE Readout Frame qualifier signal (DataValid),

- The Column Address serial information (Col\_Addr),

- The PACE Trigger FIFO Almost Full flag (FIFO\_Full).

The K-chip can identify the following error conditions in the Readout Operation of the PACE chips:

- PACE out of Sync condition is signaled when the readout sequence in one or more PACE chips is not synchronous with the K-chip internal readout operation.

- PACE Trigger FIFO almost full condition.

## 2.2 Block Diagram

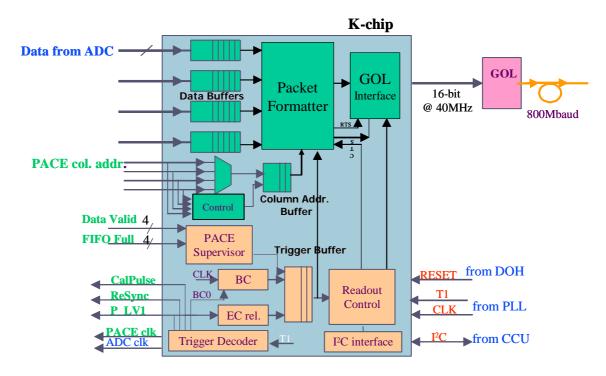

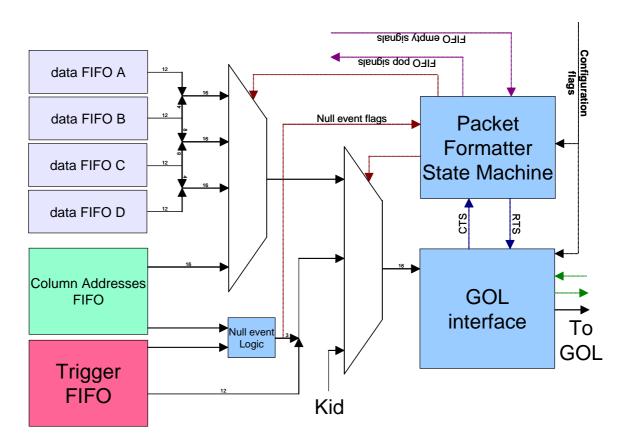

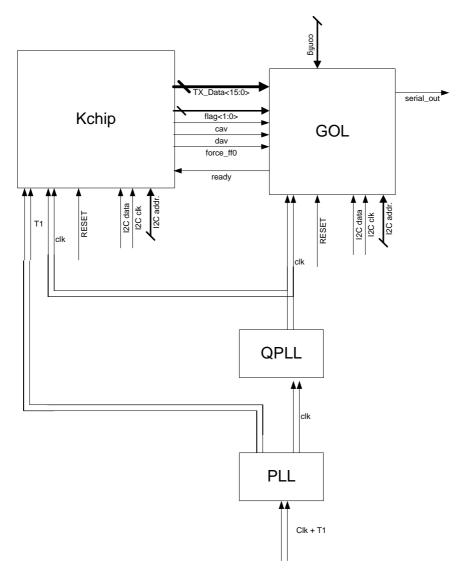

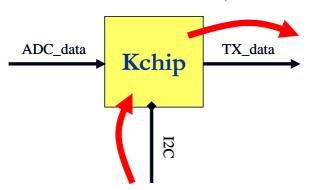

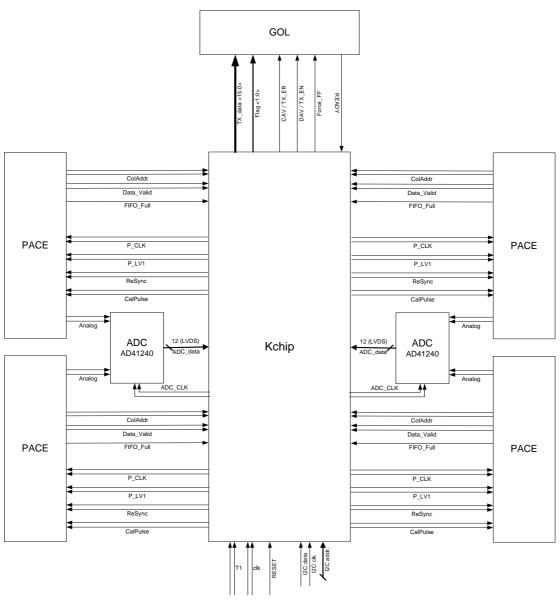

A simplified block diagram of the K-chip in the read-out system is shown in Figure 2-1.

Figure 2-1 K-chip block diagram.

The K-chip consists of the following elements:

- Four Data FIFO buffers, one per input channel to store the incoming events. These are 12-bit wide FIFOs and several events deep, see below.

- A Column Address FIFO buffer, to store the column addresses of the samples of the incoming events. This is a 16-bit wide FIFO and several events deep, see below.

- A Packet Formatter used to scan the four Data FIFOs and the Column Address FIFO when a complete event has to be assembled. The Packet Formatter also aligns the 12-bit wide data to 16-bit wide format.

- A Gigabit Optical Link Interface to encapsulate the event data with the proper header and trailer information in order to transmit them through the optical link.

- A 12-bit Bunch Counter (BC) used to count continuously the incoming 40MHz system clock.

- An 8-bit Event Counter (EC) used to count the number of incoming LV1 triggers.

- A Trigger Decoder circuit in order to decode the Trigger Commands that are received through the T1 signal from the PLL chip.

- A Trigger FIFO used to store incoming triggers while the readout of a previous event is in progress

- A control logic to provide the synchronization of the entire ASIC and the supervision of the sequence of operations necessary to build an event in the output buffer.

- A PACE Readout Supervisor logic that monitors the synchronicity of the readout operation of the PACE chips that are connected to the Kchip.

- A set of user registers, accessible through the chip's slow control port (I<sup>2</sup>C). The uses of these registers are to control and read back status information from the K-chip. They provide also the possibility to the user to write some pseudo-event data into the data FIFOs to test the functionality of the readout chain.

- An I<sup>2</sup>C based slow control interface used to access the K-chip internal registers and data FIFOs.

The simplified protocol followed by the K-chip to assemble one event into its output buffer is the following:

- the K-chip monitors continuously the state of its trigger FIFO

- when a trigger is pending in the trigger FIFO, the Packet Formatter extracts it together with the bunch counter tag which was stored in it at the moment of the arrival of the trigger signal and stores this in the header of the outgoing data packet with the K-chip ID number

- the data blocks at the head of the four input FIFOs are read and moved to the GOL interface.

- a CRC is computed and appended to the event data packet

- the packet is streamed out through the high speed readout link.

## 2.3 Operation Modes

The K-chip can be initialized in two modes:

- normal read-out mode

- link test mode

In the first mode, the K-chip assembles event blocks as described above and it used in the normal data acquisition chain. In the link test mode, the K-chip can send out data which can be written into its input FIFOs via the slow control interface. This mode is used essentially as an aid to debug a malfunctioning link outside of the normal data acquisition mode

#### 2.4 PACE Interface

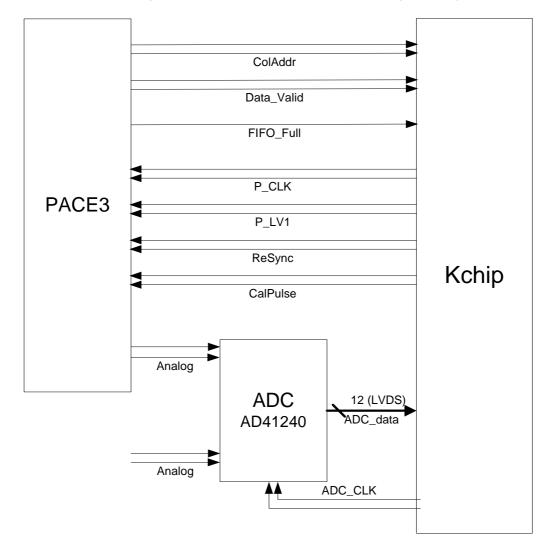

The Kchip is designed to interface with the PACE3 analog memory chip.

Figure 2-2 PACE3 to Kchip interface.

#### 2.5 ADC interface

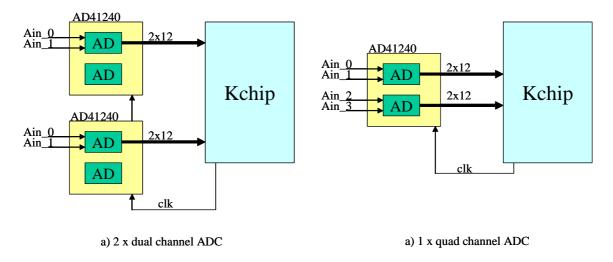

The Kchip is designed to interface with the AD41240 12bit-40Msample/s ADC, which is fabricated in the same  $0.25\mu m$  CMOS technology as the Kchip. The AD41240 is a quad channel ADC with the possibility to power down individually its channels. The AD41240 has 2 12-bit data busses. On each data bus two ADC channels are multiplexed using the Double Data Rate technique.

The Kchip offers two possibilities to interface with the ADC as shown in Figure 2-3. In option (a) it is using two dual channel ADCs while in option (b) it is using a single quad channel ADC. The final choice will be made taking into account the

general system aspects (motherboard design, ADC channel to channel crosstalk, noise, cost ....). The Kchip has a single LVDS clock output for the ADC.

Figure 2-3 Two options for interfacing the Kchip with the AD41240 ADC chip.

## 2.6 Trigger Decoder

The encoded trigger uses three consecutive bits in the T1 stream to specify different conditions according to the following table:

| Pattern | Command                              |

|---------|--------------------------------------|

| 100     | LV1A (Trigger Level 1 Accept)        |

| 101     | BC0 (Bunch Crossing Zero identifier) |

| 110     | ReSync (Reset FE Pipelines)          |

| 111     | CalPulse (Calibration)               |

Table 2-1 Coding of the Trigger Commands.

The actions taken by the Kchip logic when a Trigger Command is issued are listed below.

- LV1A: sends an trigger pulse to the PACE3 chip and increments the EC and inserts a normal event in the trigger FIFO.

- CalPulse: send a calibration pulse to the PACE3 chip and starts countdown of the latency counter. Upon timeout it increments the EC and inserts a calibration event in the Trigger FIFO.

- **ReSync:** resets the EC and BC and clears the Data, Column and Trigger FIFOs. Resets PACE supervisor logic error flags.

- **BCO**: resets the EC and BC counters.

## 2.7 K-chip Buffers

The Kchip has three different types of buffers;

- The **Data FIFO** for storing the digitized samples of the trigger events. There are four identical Data FIFOs, one for each Kchip input channel.

- The **Column Address FIFO** for storing the column addresses that correspond to the trigger events stored in the Data FIFO. There are four identical Column Address FIFOs, one for each Kchip input channel.

- The **Trigger FIFO** for storing the time tags (Bunch counter, event Counter) and control information of the incoming triggers. There is one Trigger FIFO in the Kchip.

#### 2.7.1 Buffer Sizes

The size of the input buffers in the K-chip determines the probability of losing an event because of a momentary congestion.

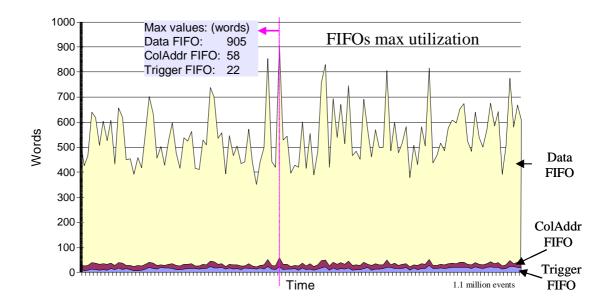

Using a software emulation model of the system we have determined the size of the three different buffer types. The simulation results are shown in Figure 2-4.

Figure 2-4 Simulation results of the Kchip at 100KHz trigger rate presenting the traffic in the Data FIFO, Column FIFO and Trigger FIFO.

The FIFO sizes implemented in the Kchip are listed in Table 2-2.

Table 2-2 FIFO sizes in the Kchip.

| FIFO           | Size                |

|----------------|---------------------|

| Data           | 1 Kword x 18 bits   |

| Column Address | 128 words x 27 bits |

| Trigger        | 128 words x 27 bits |

#### 2.7.2 Data FIFO

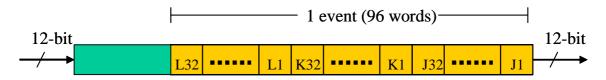

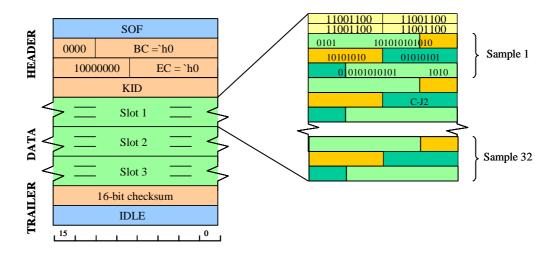

The format of the information stored in the Data FIFOs is shown in Figure 2-5.

Memory Slots per event: J,K,L

Samples per slot: 1..32

Figure 2-5 Format of the information stored in the Data FIFOs.

Having a size of 1Kword, the Data FIFO can store up to 10 events (1024/96).

#### 2.7.3 Column Address FIFO

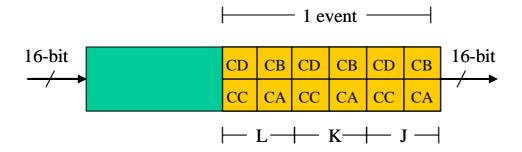

The format of the information stored in the Column FIFOs is shown in Figure 2-6.

Memory Slots per event: J,K,L

Samples per slot: 1..32

Figure 2-6 Format of the information stored in the Column FIFOs.

#### 2.7.4 Trigger FIFO

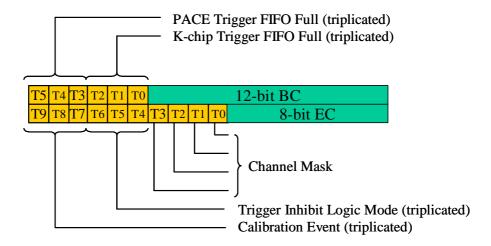

The format of the trigger events stored in the Trigger FIFO is shown in Figure 2-7.

Figure 2-7 Record of an Event in the Trigger FIFO (18-bits wide).

Having a size of 128words, the Trigger FIFO can store up to 64 triggers (128/2).

The Trigger FIFO is seen by the user as a 14-bits wide FIFO. Actually is 18-bits wide but the 6 MSBs are used in a triplicated manner to code two bits, see Figure 2-7.

## 2.8 PACE supervisor

The Kchip provides a mechanism for checking the synchronicity of the operation of the four PACE chips that are attached to its input channels. The mechanism is using a cycle-by-cycle comparison of the PACE readout control signals with the Kchip internally generated control signals. The results of the comparison are flagged in the Event Data Packet transmitted on the Data Link and in the Kchip Status Register.

There are two readout control signals generated by the PACE chip:

- The **DataValid** signal that indicates the boundaries of the events as transmitted by the PACE chip.

- The **PACE FIFO Almost Full** signal that indicates the availability of free locations in the PACE Trigger FIFO for storing more trigger events.

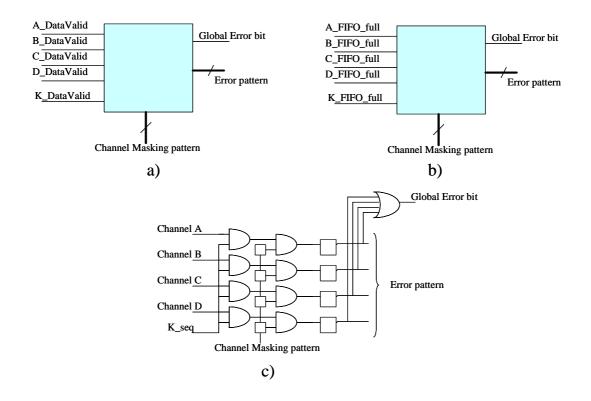

These readout signals are individually compared with the Kchip internally generated readout signals as shown in Figure 2-8. The logic of the comparison is common for the two signals.

Figure 2-8 a) Comparison logic for the DataValid signal, b) comparison logic for the PACE FIFO Almost Full signal, c) schematic diagram of the comparison logic.

## 2.9 Kchip Data Path design

Figure 2-9 The Kchip Data Path.

## 2.10 Error Conditions / Error handling

#### 2.10.1 Buffer Overflows

#### 2.10.2 Synchronization of PACE3 chips

#### 2.11 Packet Formatter

#### 2.11.1 Link Data Packet Format

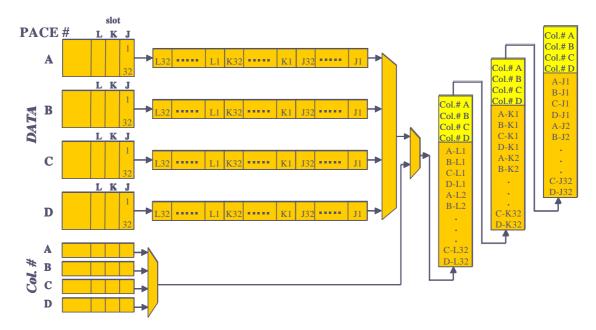

Figure 2-10 shows the mechanism that the K-chip employs to rearrange the incoming data in the four input channels.

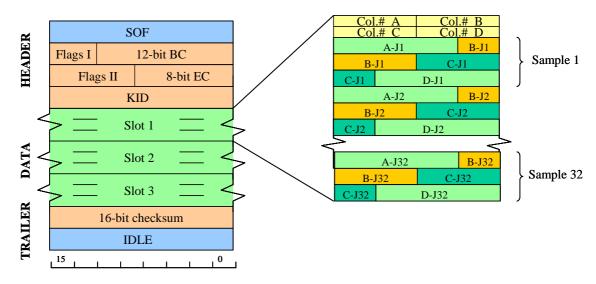

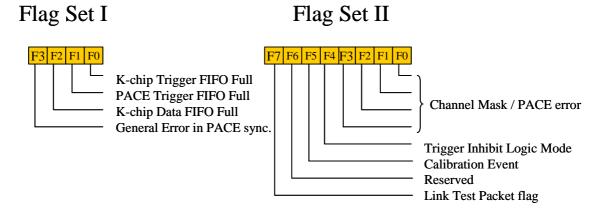

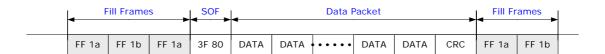

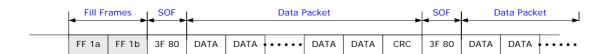

The format of the data transmitted through the High Speed Link is shown in Figure 2-11 & Figure 2-12.

Figure 2-10 Mechanism for the Event Data Formatting.

Figure 2-11 Link Data Packet Format.

Figure 2-12 Link Data Packet Format.

Table 2-3 Explanation of the flags in the data packet.

| Flag                    | Function                                                                                 |

|-------------------------|------------------------------------------------------------------------------------------|

| Kchip Trigger FIFO full | This flag is set only in NULL events.                                                    |

| PACE Trigger FIFO full  | This flag is set only in NULL events.                                                    |

| Kchip Data FIFO full    | This flag is set only in NULL events.                                                    |

| General Error in PACE   | When this bit is set to '1' it indicates that a PACE synchronization error has occurred. |

| Channel Mask / PACE   | When the "General Error in PACE" flag is set to '0'                                                                                                                                                |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| error                 | these four bits indicate the active data channels in the Kchip.                                                                                                                                    |

|                       | When the "General Error in PACE" flag is set to '1' these four bits indicate the corresponding channel(s) that has the PACE chip(s) found to be out of sync.                                       |

| Trigger Inhibit Logic | When this bit is set to '1' it indicates that the Trigger Inhibit logic in the Kchip is ENABLED. When this bit is set to '0' it indicates that the Trigger Inhibit logic in the Kchip is DISABLED. |

| Calibration Event     | When this bit is set to '1' it indicates that the current data packet being transmitted belongs to a Calibration Event.                                                                            |

| Link Test Packet      | When this bit is set to '1' it indicates the transmission of a packet for link test purposes.                                                                                                      |

#### Normal Event Null Event SOF SOF HEADER HEADER Flags I 12-bit BC Flags I 12-bit BC Flags II 8-bit EC Flags II 8-bit EC KID KID TRAILER 16-bit checksum Slot 1 **IDLE** Slot 2 Slot 3 TRAILER 16-bit checksum IDLE 15

Figure 2-13 Packet Format of the Normal Event and the Null Event.

The Link Data Packet starts with a <u>Header Field</u> followed by the <u>Data Payload</u> and ends with a Trailer Field.

The Header Field consists of:

- a Start Of Frame (SOF) word which is used to synchronize the readout operation

- two sets of Flags of 12-bits in total for signaling the type of Data Packet and various Error Conditions

- an 8-bit Event Counter (EC)

- a 12-bit Bunch Counter (BC)

- a 16-bit K-chip IDentification number (KID)

The <u>Data Payload Field</u> consists of 3 identical data packets each containing information coming from a time slot. Each time slot data packet contains:

- the column addresses of the 4 PACE chips

- the 12-bit digitized values of the 36 data samples contained in one PACE column.

- The <u>Trailer Field</u> consists of:

- A 16-bit Cyclic Redundancy Checksum word as calculated over the whole information in the data packet except the SOF and EOF words. The CRC field is calculated following the CRC-16 algorithm.

- An End Of Frame (EOF) word, which is used to signal the end of the data packet.

The size of one **SLOT** in the Data Packet can be calculated as follows:

$(4 \text{ PACEs x } 32 \text{ samples x } 12\text{-bit})/(16\text{-bit}) + 2 \text{ words } (column \ address) = 98 \text{ words } 616\text{-bit}.$

The size of the **Data Payload** is then: 3 slots x 98 words = 294

The size of the **Normal Data Packet** is then calculated as:

4 words (Header) + 294 words + 1 words (Trailer) = 299 words.

## 2.12 Gigabit Link Interface

#### 2.12.1 Physical Layer

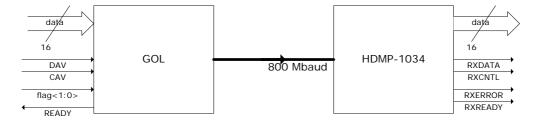

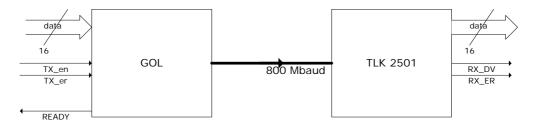

The Kchip is designed to interface with the Gigabit Optical Link (GOL) chip. The Kchip – GOL interface runs at 40MHz over a 16-bit bus thus allowing a net data throughput of 640Mbps or 80Mbyte/sec.

In the case where the quality (amount of jitter) of the clock signal provided by the Tracker PLL is inadequate to operate the GOL chip the possibility of using a PLL employing a crystal oscillator (QPLL) is foreseen. Figure 2-14 shows the Kchip GOL chip interfacing.

Figure 2-14 Kchip - GOL chip interface employing the QPLL for clock generation.

#### 2.12.2 Link Layer

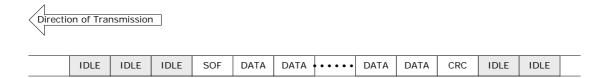

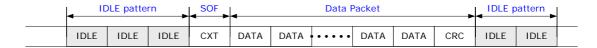

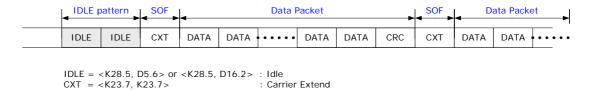

The Kchip employs a character oriented data transmission protocol. To achieve character synchronization the Kchip uses two uniquely defined transmission control characters, the IDLE and the SOH. The general data frame format is shown in Figure 2-15.

The IDLE character has two functions. Firstly, allows the receiver to obtain and maintain bit synchronization. Secondly, once bit synchronization has been acquired, allows the receiver to start to interpret the received bit stream on the correct character boundaries thus obtaining character synchronization.

The SOF character indicates the beginning of the frame and delimits the boundaries of subsequently transmitted frames (back-to-back transmission). Once the receiver has obtained character synchronization (and hence reading each character on the correct bit boundary), the receiver starts to process subsequently received character in search of the SOH character indicating the start of the frame. On receipt of the SOF character, the receiver proceeds to receive the frame contents and terminates this process.

#### **General Frame Format**

Figure 2-15 General Frame format.

The GOL chip supports two encoding schemes for the transmitted data, the CMIT protocol and the 8b/10b encoding protocol. The Kchip can seamlessly use both of the two transmission schemes without the need of any modification in the wiring or configuration register programming. To select the encoding scheme the user has to configure the mode selection pin of the GOL chip.

The flexibility of using both encoding schemes is realized by properly choosing the transmission control symbols (SOF, IDLE) which are supported in both encoding schemes and by implementing a link synchronization mechanism that can be applied in common for the two deserializers types used in the two encoding schemes.

The Kchip data transmission protocol employs an Error Detection mechanism to identify errors that can occur on the data links. The error detection mechanism is based on the transmission of a frame check sequence character placed at the end of the data frame. The frame check sequence character is a 16-bit CRC for the complete frame contents enclosed from the SOF character to the end of the frame. The CRC (Cyclic Redundancy Checking) generator polynomial in use is the CRC-CCITT:  $x^{16} + x^{12} + x^5 + 1$ .

#### 2.12.3 Using CIMT protocol

Figure 2-16 Link structure (serializer-deserializer) when using CIMT protocol.

Figure 2-17 Packet format in CIMT protocol.

Figure 2-18 Packet format in CIMT protocol for back-to-back events.

## 2.12.4 Using 8b/10b encoding protocol

Figure 2-19 Link structure (serializer-deserializer) when using 8b/10b encoding protocol.

Figure 2-20 Packet format in 8b/10b protocol.

Figure 2-21 Packet format in 8b/10b protocol for back-to-back events.

### 2.13 Link Synchronization Issues

The only way to synchronize the transmitter – receiver pair on the data links is to force the transmission of a stream of IDLE characters.

Transmission of IDLE characters commences:

- After hardware RESET has been issued and will last until data are present for transmission.

- After a ReSync has been issued and will last until data are present for transmission.

- When the "FORCE\_IDLE" bit is asserted in the packet formatter.

- While the "GOL\_READY" bit is de-asserted in the "STATUS\_0" register.

- When the programmable counter (counting transmitted data packets) time outs. A sync pattern of programmable length is transmitted in programmable intervals.

#### 2.13.1 Link Test Mode

A special "Link Test Mode" is implemented in the Kchip logic in order to facilitate the testing of the Gigabit Optical Links connecting the Kchips with the off-detector electronics.

# Link Test Packet

Figure 2-22 Format of the Link Test Packet.

#### 2.14 Calibration Circuit

#### 2.14.1 The DLL circuit

The DLL block gets reset upon ResetB signal going low and upon a ReSync command.

#### 2.14.2 Generating and Reading out calibration events.

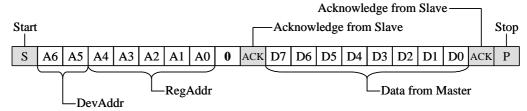

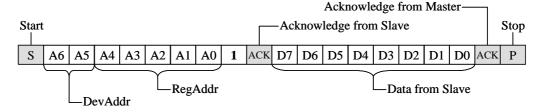

## 2.15 I<sup>2</sup>C Interface

The Kchip has a slow control interface following the  $I^2C$ -bus PHILIPS standard. This is specified completely in the PHILIPS datasheet and is not described here. The Kchip I2C interface allows for **7-bit addressing single byte transfers**. The format of the Read and Write access cycles that can be targeted to the Kchip are shown in Figure 2-23. Table 2-4 shows the bit assignment for the address field of the  $I^2C$  bus transactions. Incremental Read or Write accesses without retransmitting the address field are not possible.

The Kchip I<sup>2</sup>C slave interface is implemented using synchronous logic clocked at 40MHz. A synchronizer circuit is employed in the SCA SDA signals to alleviate any metastability problems.

#### Write Access

#### **Read Access**

Slave is the Kchip Master is the CCU chip

Figure 2-23 Write and Read access cycles through the Kchip I<sup>2</sup>C bus.

Table 2-4 Bit assignment for the address field of the I<sup>2</sup>C bus transactions.

| Bits <6:0> | Name         | Comments                                                     |

|------------|--------------|--------------------------------------------------------------|

| 4:0        | RegAddr<4:0> | Selects the location in the Internal Register address space. |

| 6:5        | DevAddr<1:0> | Sets the Device Address on the I <sup>2</sup> C bus.         |

## 3 SEU Tolerant Techniques

#### 3.1 General Architecture

The Kchip will have to operate in a radiation environment where the flux of energetic particles that can cause Single Event Upsets (SEUs) is high.

The design guidelines for the Kchip are:

To protect the **Control Logic** circuitry using Triple Module Redundancy. SEUs in the Kchip control logic would cause loss of synch that can only be recovered by resetting the Kchip. To avoid the need of frequent resets it is necessary that we protect as much as possible the operation of all the Kchip State Machines and the configuration registers.

To leave the **Data Path** unprotected. The triplication of the Kchip Data Path is not foreseen since the errors created by the SEU will affect the integrity of a small amount of information being processed at the time of the SEU incidence and will not lead to a loss of sync of the Kchip operation.

#### 3.2 State Machines

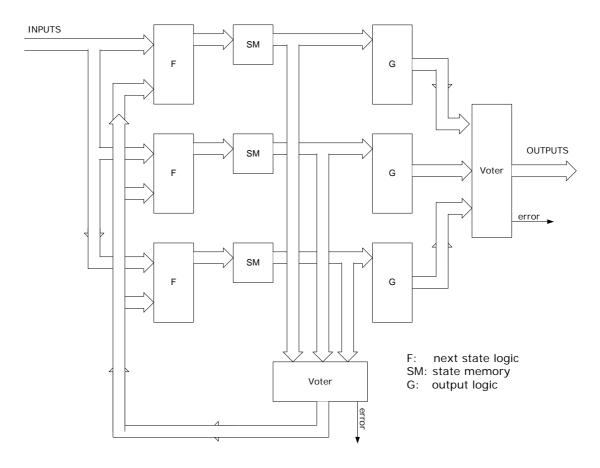

The implemented Triple Module Redundancy scheme for the Kchip state machines is shown in Figure 3-1.

Figure 3-1 Triple Module Redundancy for the Kchip State Machines.

## 3.3 Configuration Registers

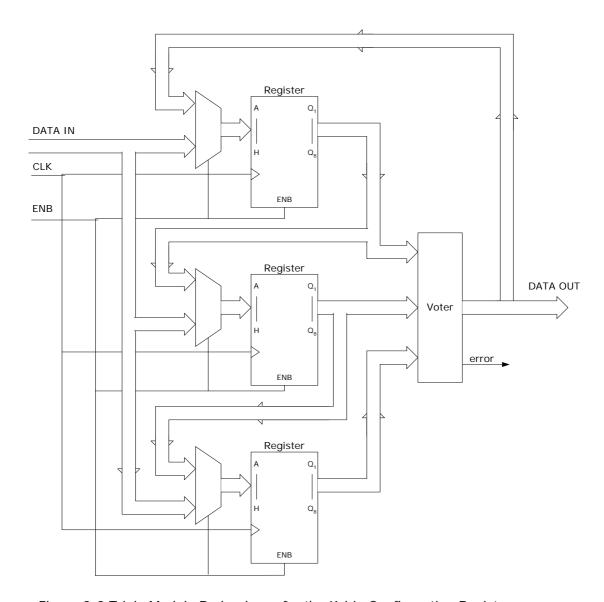

The implemented Triple Module Redundancy scheme for the Kchip configuration registers is shown in Figure 3-2.

Figure 3-2 Triple Module Redundancy for the Kchip Configuration Registers.

## 3.4 The SEU\_COUNTER

The error signals from all the Triplicated Modules are ORed together to provide a global error signal. This signal is fed to a synchronous counter that is clocked from the 40MHz system clock. The counter value will indicate the number of Single

Event Upsets encountered on all the Triplicated Modules on the Kchip since the last hardware reset. The SEU\_COUNTER is accessible through the  $I^2C$  bus.

Optionally the SEU\_COUNTER can be used as a tool for the production testing of the Kchip. The chips having a production fault can be detected by checking that the contents of the SEU\_COUNTER are constantly changing.

# 4 Internal Registers

The Table 4-1 specifies the registers (all 8-bit wide) accessible via the I2C interface in the K-chip (double registers are tagged with a \_H-L name).

Table 4-1 K-chip Internal Registers

| Name        | I <sup>2</sup> C<br>Address | Function                                                                                                                                                         | Туре |

|-------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CONFIG      | 0                           | This register contains various configuration and mode fields as specified below.  Default value: 8`b00001111                                                     | R/W  |

| ECONFIG     | 1                           | This extra-configuration register contains various configuration and mode fields as specified below.  Default value: 2`b00                                       | R/W  |

| KID_H-L     | 3-2                         | K-chip ID register. Default value: 16`b000000000000000xx                                                                                                         | R/W  |

| MASK_T1CMD  | 4                           | This register contains a 4 bit mask pattern for the Trigger Commands.  Default value: 4'b0000                                                                    | R/W  |

| LAST_T1CMD  | 5                           | A read operation from this register returns the last issued Trigger Command.                                                                                     | RO   |

| LATENCY     | 6                           | This register sets the Trigger Latency value, in clock cycles, for generating a readout cycle after a Calibration command has been issued.  Default value: 'd128 | R/W  |

| EVCNT       | 7                           | A read operation from this register gives<br>the 8 bit current content of the Event<br>Counter in the K-chip                                                     | RO   |

| BNCHCNT_H-L | 9-8                         | A read operation from this register returns the 12 bit bunch counter value used to tag the last event.                                                           | RO   |

| RESERVED    | А                           |                                                                                                                                                                  |      |

| GINT_BUSY   | В                           | This register contains the timeout period for transmitting a synchronization pattern by the GOL interface.  Default value: `d0                                   | R/W  |

| GINT_IDLE   | С                           | This register contains the length of the synchronization pattern in the GOL interface.  Default value: `d0                                                       | R/W  |

| FIFOMAP     | D                           | This register contains a pointer to one of the FIFOs in the chip, it is used to direct read/write operations to the corresponding FIFO                           | R/W  |

| FIFODATA_H-L   | E-F | When in Link Test mode, writing to this register causes data to be written into the FIFO pointed to by the FIFOMAP register; a read operation instead reads data from the corresponding FIFO. When in normal mode, read/write operations to this | R/W |

|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                |     | register are ignored.                                                                                                                                                                                                                            |     |

| STATUS_0       | 10  | This register contains a number of status bits as specified below. It is reset upon a ReSync command.                                                                                                                                            | RO  |

| STATUS_1       | 11  | This register contains a number of status bits as specified below. It is reset upon a ReSync command.                                                                                                                                            | RO  |

| SEU_COUNTER    | 12  | This register contains the total number of single Events Upsets encountered on the chip since the last hardware RESET.                                                                                                                           | RO  |

| CalPulse_DELAY | 13  | This register contains the delay period for generating a PACE calibration pulse.  Default value: `d1                                                                                                                                             | R/W |

| CalPulse_WIDTH | 14  | This register contains the width period of the PACE calibration pulse.  Default value: `d1                                                                                                                                                       | R/W |

| ADC_LATENCY    | 15  | This 4-bit register contains the number of ADC latency clock cycles.                                                                                                                                                                             | R/W |

|                |     | Default value: 4`d5                                                                                                                                                                                                                              |     |

| PFIFO_Overflow | 16  | This 6-bit register contains the overflow threshold for the PACE FIFO.                                                                                                                                                                           | R/W |

|                |     | Default value: 6`d42                                                                                                                                                                                                                             |     |

| RESERVED       | 17  |                                                                                                                                                                                                                                                  |     |

| RESERVED       | 18  |                                                                                                                                                                                                                                                  |     |

| RESERVED       | 19  |                                                                                                                                                                                                                                                  |     |

| RESERVED       | 1A  |                                                                                                                                                                                                                                                  |     |

| RESERVED       | 1B  |                                                                                                                                                                                                                                                  |     |

| RESERVED       | 1C  |                                                                                                                                                                                                                                                  |     |

| RESERVED       | 1D  |                                                                                                                                                                                                                                                  |     |

| SID_L          | 1E  | This two registers are hardwired to the                                                                                                                                                                                                          | RO  |

| SID_H          | 1F  | serial ID number written in the fuses.                                                                                                                                                                                                           | RO  |

## 4.1.1 The CONFIG Register

Table 4-2 *Config* register bit assignment.

| <u> </u>                                              |   | 1                                                                                                                                                                                                                            |

|-------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KchipMode                                             | 7 | Determines if the K-chip is in normal or test mode.  A 0 in this bit corresponds to NORMAL mode  A 1 in this bit corresponds to TEST mode.  The bit is reset to 0 after an external reset to the Kchip.                      |

| TriggerInhibitMode 6 Determ A 0 in t A 1 in t The bit |   | Determines the mode of the Trigger Inhibit logic.  A 0 in this bit sets the logic into the INHIBIT mode.  A 1 in this bit sets the logic into the PASSIVE mode.  The bit is reset to 0 after an external reset to the Kchip. |

| TX_EnableB                                            | 5 | Controls the data transmission through the GOL link.  A 0 in this bit ENABLES the data transmission.  A 1 in this bit DISABLES the data transmission.  The bit is reset to 0 after an external reset to the Kchip.           |

| Link_Test                                             | 4 | Link Test Mode.  A 0 in this bit enables the normal data transmission.  A 1 in this bit sets the chip in the link test mode.  The bit is reset to 0 after an external reset to the Kchip.                                    |

| ChannelEnable_D                                       | 3 |                                                                                                                                                                                                                              |

| ChannelEnable_C                                       | 2 |                                                                                                                                                                                                                              |

| ChannelEnable_B                                       | 1 |                                                                                                                                                                                                                              |

| ChannelEnable_A 0                                     |   |                                                                                                                                                                                                                              |

## 4.1.2 The *ECONFIG* Register

Table 4-3 *ECONFIG* register bit assignment.

| Name          | Position | Function                                                                                                                                                                                                                                                |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 7        |                                                                                                                                                                                                                                                         |

|               | 6        |                                                                                                                                                                                                                                                         |

|               | 5        |                                                                                                                                                                                                                                                         |

|               | 4        |                                                                                                                                                                                                                                                         |

|               | 3        |                                                                                                                                                                                                                                                         |

|               | 2        |                                                                                                                                                                                                                                                         |

| Mask_CalEvent | 1        | Controls the automatic generation of calibration events after the "latency" period following the issue of a Calibration Trigger Command.  A 0 in this bit ENABLES the generation of Cal_Events.  A 1 in this bit DISABLES the generation of Cal_Events. |

| DLL_Off | 0 | Enables or Disables the DLL logic.      |

|---------|---|-----------------------------------------|

|         |   | A 0 in this bit ENABLES the DLL logic.  |

|         |   | A 1 in this bit DISABLES the DLL logic. |

|         |   |                                         |

## 4.1.3 The STATUS\_0 Register

Table 4-4 STATUS\_0 register pin assignment.

| Name      | Position | Function                                                                                             |

|-----------|----------|------------------------------------------------------------------------------------------------------|

| KOS       | 7        | Kchip Out of Sync. This bit sticks until the K-chip receives a ReSync command or a RESET is applied. |

| GOL_READY | 6        | This bit monitors the Gigabit Optical Link READY signal.                                             |

|           | 5        |                                                                                                      |

|           | 4        |                                                                                                      |

|           | 3        |                                                                                                      |

|           | 2        |                                                                                                      |

|           | 1        |                                                                                                      |

|           | 0        |                                                                                                      |

## 4.1.4 The STATUS\_1 Register

Table 4-5 *STATUS\_1* register pin assignment.

| Name   | Position | Function                                                                                                                                                                                                                                 |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROS_D | 7        | PACE Readout Out-of-Sequence                                                                                                                                                                                                             |

|        |          | This bit is set when the PACE corresponding to input channel D has delivered a DataValid signal that does not follow a correct readout cycle sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied. |

| PROS_C | 6        | PACE Readout Out-of-Sequence                                                                                                                                                                                                             |

|        |          | This bit is set when the PACE corresponding to input channel C has delivered a DataValid signal that does not follow a correct readout cycle sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied. |

| PROS_B | 5        | PACE Readout Out-of-Sequence                                                                                                                                                                                                             |

|        |          | This bit is set when the PACE corresponding to input channel B has delivered a DataValid signal that does not follow a correct readout cycle sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied. |

| PROS_A | 4 | PACE Readout Out-of-Sequence This bit is set when the PACE corresponding to input channel A has delivered a DataValid signal that does not follow a correct readout cycle sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied. |

|--------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFOS_D | 3 | PACE FIFO Out-of-Sequence                                                                                                                                                                                                                                             |

|        |   | This bit is set when the PACE corresponding to input channel D has delivered an Almost_Full FIFO signal that does not follow a correct sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied.                                    |

| PFOS_C | 2 | PACE FIFO Out-of-Sequence                                                                                                                                                                                                                                             |

|        |   | This bit is set when the PACE corresponding to input channel C has delivered an Almost_Full FIFO signal that does not follow a correct sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied.                                    |

| PFOS_B | 1 | PACE FIFO Out-of-Sequence                                                                                                                                                                                                                                             |

|        |   | This bit is set when the PACE corresponding to input channel B has delivered an Almost_Full FIFO signal that does not follow a correct sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied.                                    |

| PFOS_A | 0 | PACE FIFO Out-of-Sequence                                                                                                                                                                                                                                             |

|        |   | This bit is set when the PACE corresponding to input channel A has delivered an Almost_Full FIFO signal that does not follow a correct sequence. This bit sticks until the K-chip receives a ReSync command or a RESET is applied.                                    |

## 4.1.5 The FIFOMAP Register

Table 4-6 FIFOMAP bit assignment.

| Bits <5:0> | Мар                                    |  |

|------------|----------------------------------------|--|

| 5          | R/W operations to Trigger FIFO.        |  |

| 4          | R/W operations to Column Address FIFO. |  |

| 3          | R/W operations to Data FIFO channel D  |  |

| 2          | R/W operations to Data FIFO channel C  |  |

| 1          | R/W operations to Data FIFO channel B  |  |

| 0          | R/W operations to Data FIFO channel A  |  |

## 4.1.6 The FIFODATA Register

This 16 bit register is used to write 12 bits of data into the FIFO pointer to by the FIFOMAP register. The write operation actually occurs when the FIFODATA\_L

register is written. A read operation reads the last in the FIFO and decrements by one the number of words in it.

### 4.1.7 The EVNCNT Register

This Read-Only register return the value of the Event Counter associated with the last occurrence of a Level 1 trigger

### 4.1.8 The BNCHCNT Register

This Read-Only registers returns the value of the Bunch Counter associated with the last occurrence of a Level 1 trigger.

### 4.1.9 The MASK\_T1CMD Register

This Read-Write register sets a mask pattern in the Trigger Decoder logic which can be used to individually enable or disable the decoding of trigger commands.

| Bits <3:0> | Мар                                                |  |

|------------|----------------------------------------------------|--|

| 3          | A 1 in this bit masks the <b>BCO</b> command.      |  |

| 2          | A 1 in this bit masks the <b>CalPulse</b> command. |  |

| 1          | A 1 in this bit masks the <b>ReSync</b> command.   |  |

| I          | A i in this bit masks the <b>Resync</b> command.   |  |

A 1 in this bit masks the **LV1** command.

Table 4-7 MASK\_T1CMD bit assignment.

## 4.1.10 The LAST\_T1CMD Register

This Read-Only register returns the type of the last Trigger Command that was received and decoded by the Trigger Decoder logic.

Bits <3:0> Map

3 A 1 in this bit indicates a BC0 command.

2 A 1 in this bit indicates a CalPulse command.

1 A 1 in this bit indicates a ReSync command.

0 A 1 in this bit indicates an LV1 command.

Table 4-8 LAST\_T1CMD bit assignment.

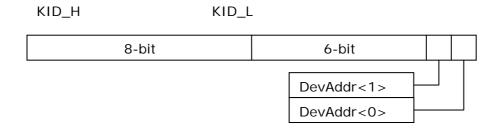

## 4.1.11 The KID Register

This Read-Write 16-bit register sets the Kchip Identification number. The least significant part of the register (KID\_L) is composed by the two hardwired pins that

define the Kchip slave interface in the I2C bus and 6-bits that are accessible by the user. The format of the KID register is shown in the figure below.

The KID is transmitted with every event data packet.

### 4.1.12 The *LATENCY* Register

This Read-Write register sets the latency value in clock cycles for initiating the readout cycle of the calibration event.

## 4.1.13 The *GINT\_BUSY* Register

This Read-Write register sets the timeout period of continuously transmitted event data without intermittent IDLE characters. The timeout period is defined in number of event data packets. For examples refer to Table 4-10.

### 4.1.14 The *GINT\_IDLE* register

This Read-Write register sets the length of the link synchronization pattern (SYNC pattern). The length is defined in number of IDLE characters. For examples refer to Table 4-9.

Table 4-10 Possible combinations for the GINT\_BUSY and GINT\_IDLE registers.

| GINT_BUSY | GINT_IDLE | Result                                                 |  |

|-----------|-----------|--------------------------------------------------------|--|

| 0         | 0         | No IDLE characters are inserted.                       |  |

| 0         | 1         | No IDLE characters are inserted.                       |  |

| 1         | 0         | No IDLE characters are inserted.                       |  |

| 1         | 1         | One IDLE character is inserted in every DATA PACKET.   |  |

| 1         | 2         | Two IDLE characters are inserted in every DATA PACKET. |  |

| 2         | 1         | One IDLE character is inserted every two DATA PACKETs. |  |

### 4.1.15 The CalPulse\_DELAY register

This register contains the DLL configuration byte for generating a PACE calibration pulse. By setting this register the user can modify the delay of the calibration pulse by a fraction of a clock cycle. This byte is one-cold encoded; therefore only one bit must be zero while all the other ones must be one. The position of the zero bit determines the delay of the line: if the lsb is zero the delay is minimum, while if the msb is zero the delay is maximum. The default value for this register is `b11111110 which gives the minimum delay.

### 4.1.16 The CalPulse\_WIDTH register

This register contains the width period of the PACE calibration pulse expressed in clock cycles. The actual pulse will be one clock cycle wider than the value stored in the register. The minimum value for this register is 2, which is also the default value, and to which corresponds a pulse width of 3 clock cycles. The maximum value is 255 which gives a pulse width of 256 clock cycles. Setting a value lower than the minimum allowed will cause the DLL to malfunction.

### 4.1.17 The *ADC\_LATENCY* register

This register must be set to the ADC latency expressed in clock cycles. The Kchip calculates the validity of the data on the ADC output bus by looking at this value. The register maximum value is 31. The default is 5.

### 4.1.18 The *PFIFO\_Overflow* register

This register must contain the threshold used in the PACE chip to evaluate the PACE FIFO almost full flag. The Kchip makes an internal copy of this flag based on the value of PFIFO\_Overflow, and it is then compared to the external ones in order to verify the PACE synchronicity. Moreover, if TriggerInhibitMode=0, when the internal PACE FIFO almost full flag is 1 the Kchip doesn't send triggers to the PACE to prevent overflows.

### 4.2 Event reading/writing through I2C

### 4.2.1 Event writing through I2C

In order to write an event through the I2C interface the CONFIG register has to be first set to 'b10101111 which poses KchipMode=1 and TX\_EnableB=1, allowing the FIFOs to be written via I2C and disabling the output blocks of the chip. After this the FIFOs can be filled as described in Section **Error! Reference source not found.**. Then the CONFIG register has to be restored to its original configuration 'b00001111 to re-activate the output blocks and the readout.

### 4.2.2 Event reading through I2C

It is also possible to read an event, which was normally readout by the front-end, via I2C interface. To do that is necessary to disable the output stages of the Kchip before sending the level-1 trigger by setting the CONFIG register to 'b00101111. After the data has fully arrived in the Kchip (~300 clock cycles after the level-1 trigger in case of empty buffers) the CONFIG register can be set to 'b101011111 to disable the readout and enable the I2C read/write capability to the FIFOs. Following the procedure described in Section **Error! Reference source not found.** it is possible to read the FIFOs. When finished, the CONFIG register must be put into its default state 'b00001111. In case of empty buffers at the beginning

of the operation, the first header word will be missing, only the second will be present in the Trigger FIFO.

# **5 Operating Conditions**

# **5.1 Recommended Operating Conditions**

|                                               | MIN                  | TYP  | MAX  | Unit |

|-----------------------------------------------|----------------------|------|------|------|

| V <sub>DD</sub> Supply Voltage                | 2.25                 | 2.50 | 2.75 | V    |

| VI <sub>H</sub> High Level Input Voltage      | V <sub>DD</sub> -0.2 | 5    |      | V    |

| V <sub>IL</sub> Low Level Input Voltage       |                      |      | 0.50 | V    |

| T <sub>A</sub> Operating Free-Air Temperature | -10                  | 25   | 75   | °C   |

# **6 Timing Characteristics**

Soon to come.

# 7 Packaging

Soon to come.

# 8 Pin Assignments

Table 8-1 Pin assignments sorted by pin functionality.

| DIN                                 | # Name                        | Туре        | Description                          |

|-------------------------------------|-------------------------------|-------------|--------------------------------------|

| PIN # Name PACE/ADC Interface Chann |                               |             | Description                          |

| 1                                   | AB_ADC_pos<0>                 | LVDS input  | Channel A & Channel B ADC data       |

| 2                                   | AB_ADC_pos<0> AB_ADC_neg<0>   | LVD3 IIIput | inputs.                              |

| 3                                   | AB_ADC_pos <1>                |             | inputs.                              |

| 4                                   | AB_ADC_pos <1> AB_ADC_neg <1> |             |                                      |

| 5                                   | AB_ADC_pos <2>                |             |                                      |

| 6                                   | AB_ADC_neg <2>                |             |                                      |

| 7                                   | AB_ADC_pos <3>                |             |                                      |

| 8                                   | AB_ADC_neg <3>                |             |                                      |

| 9                                   | AB_ADC_pos <4>                |             |                                      |

| 10                                  | AB_ADC_neg <4>                |             |                                      |

| 11                                  | AB_ADC_pos <5>                |             |                                      |

| 12                                  | AB_ADC_neg <5>                |             |                                      |

| 13                                  | AB_ADC_pos <6>                |             |                                      |

| 14                                  | AB_ADC_neg <6>                |             |                                      |

| 15                                  | AB_ADC_pos <7>                |             |                                      |

| 16                                  | AB_ADC_neg <7>                |             |                                      |

| 17                                  | AB_ADC_pos <8>                |             |                                      |

| 18                                  | AB_ADC_neg <8>                |             |                                      |

| 19                                  | AB_ADC_pos <9>                |             |                                      |

| 20                                  | AB_ADC_neg <9>                |             |                                      |

| 21                                  | AB_ADC_pos <10>               |             |                                      |

| 22                                  | AB_ADC_neg <10>               |             |                                      |

| 23                                  | AB_ADC_pos <11>               |             |                                      |

| 24                                  | AB_ADC_neg <11>               |             |                                      |

| 25                                  | A_ColAddr_pos                 | LVDS input  | Channel A Serial Column Address line |

| 26                                  | A_ColAddr_neg                 |             | from PACE.                           |

| 27                                  | A_DataValid_pos               | LVDS input  | Channel A Data Valid line from PACE. |

| 28                                  | A_DataValid_neg               |             |                                      |

| 29                                  | A_FIFO_Full                   | CMOS input  | Channel A FIFO Full flag from PACE.  |

| 30                                  | A_PACE_CLK_pos                | LVDS output | Channel A 40MHz PACE clock line.     |

| 31                                  | A_PACE_CLK_neg                |             |                                      |

| 32                                  | A_LV1_pos                     | LVDS output | Channel A PACE First Level Trigger   |

| 33                                  | A_LV1_neg                     |             | command line.                        |

| 34                                  | A_ReSync_pos                  | LVDS output | Channel A PACE Resynchronization     |

| 35                                  | A_ReSync_neg                  |             | command line.                        |

| 36                                  | A_CalPulse_pos                | LVDS output | Channel A PACE Calibration Pulse     |

| 37                                  | A_CalPulse_neg                |             | Injection command line.              |

| 38                                  | B_ColAddr_pos                 | LVDS input  | Channel B Serial Column Address line |

| 39                                  | B_ColAddr_neg                 |             | from PACE.                           |

| 40                                  | B_DataValid_pos               | LVDS input  | Channel B Data Valid line from PACE. |

| 41                                  | B_DataValid_neg               |             |                                      |

| 42 | B_FIFO_Full     | CMOS input    | Channel B FIFO Full flag from PACE.      |

|----|-----------------|---------------|------------------------------------------|

| 43 | B_PCLK_pos      | LVDS output   | Channel B 40MHz PACE clock line.         |

| 44 | B_PCLK_neg      |               | Gridinier B. Tellin IZ 1716Z Gleek inter |

| 45 | B_LV1_pos       | LVDS output   | Channel B PACE First Level Trigger       |

| 46 | B_LV1_neg       | 2120 00.100.1 | command line.                            |

| 47 | B_ReSync_pos    | LVDS output   | Channel B PACE Resynchronization         |

| 48 | B_ReSync_neg    | 2120 00.100.1 | command line.                            |

| 49 | B_CalPulse_pos  | LVDS output   | Channel B PACE Calibration Pulse         |

| 50 | B_CalPulse_neg  |               | Injection command line.                  |

| 51 | CD_ADC_pos <0>  | LVDS input    | Channel C & Channel D ADC data           |

| 52 | CD_ADC_neg <0>  | '             | inputs.                                  |

| 53 | CD_ADC_pos <1>  |               | ·                                        |

| 54 | CD_ADC_neg <1>  |               |                                          |

| 55 | CD_ADC_pos <2>  |               |                                          |

| 56 | CD_ADC_neg <2>  |               |                                          |

| 57 | CD_ADC_pos <3>  |               |                                          |

| 58 | CD_ADC_neg <3>  |               |                                          |

| 59 | CD_ADC_pos <4>  |               |                                          |

| 60 | CD_ADC_neg <4>  |               |                                          |

| 61 | CD_ADC_pos <5>  |               |                                          |

| 62 | CD_ADC_neg <5>  |               |                                          |

| 63 | CD_ADC_pos <6>  |               |                                          |

| 64 | CD_ADC_neg <6>  |               |                                          |

| 65 | CD_ADC_pos <7>  |               |                                          |

| 66 | CD_ADC_neg <7>  |               |                                          |

| 67 | CD_ADC_pos <8>  |               |                                          |

| 68 | CD_ADC_neg <8>  |               |                                          |

| 69 | CD_ADC_pos <9>  |               |                                          |

| 70 | CD_ADC_neg <9>  |               |                                          |

| 71 | CD_ADC_pos <10> |               |                                          |

| 72 | CD_ADC_neg <10> |               |                                          |

| 73 | CD_ADC_pos <11> |               |                                          |

| 74 | CD_ADC_neg <11> |               |                                          |

| 75 | C_ColAddr_pos   | LVDS input    | Channel C Serial Column Address line     |

| 76 | C_ColAddr_neg   |               | from PACE.                               |

| 77 | C_DataValid_pos | LVDS input    | Channel C Data Valid line from PACE.     |

| 78 | C_DataValid_neg |               |                                          |

| 79 | C_FIFO_Full     | CMOS input    | Channel C FIFO Full flag from PACE.      |

| 80 | C_PACE_CLK_pos  | LVDS output   | Channel C 40MHz PACE clock line.         |

| 81 | C_PACE_CLK_neg  |               |                                          |

| 82 | C_LV1_pos       | LVDS output   | Channel C PACE First Level Trigger       |

| 83 | C_LV1_neg       |               | command line.                            |

| 84 | C_ReSync_pos    | LVDS output   | Channel C PACE Resynchronization         |

| 85 | C_ReSync_neg    |               | command line.                            |

| 86 | C_CalPulse_pos  | LVDS output   | Channel C PACE Calibration Pulse         |

| 87 | C_CalPulse_neg  |               | Injection command line.                  |

| 88 | D_ColAddr_pos   | LVDS input    | Channel D Serial Column Address line     |

| 89 | D_ColAddr_neg   |               | from PACE.                               |

| 90 | D_DataValid_pos | LVDS input    | Channel D Data Valid line from PACE.     |

| 91 | D_DataValid_neg |               |                                          |

| 92     | D_FIFO_Full               | CMOS input            | Channel D FIFO Full flag from PACE.                                                                            |  |  |

|--------|---------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| 93     | D_PACE_CLK_pos            | LVDS output           | Channel D 40MHz PACE clock line.                                                                               |  |  |

| 94     | D_PACE_CLK_neg            |                       | Gridinion B. Tollin E. Prioz. Great line.                                                                      |  |  |

| 95     | D_LV1                     | LVDS output           | Channel D PACE First Level Trigger                                                                             |  |  |

| 96     | D_LV1b                    |                       | command line.                                                                                                  |  |  |

| 97     | D_ReSync_pos              | LVDS output           | Channel D PACE Resynchronization                                                                               |  |  |

| 98     | D_ReSync_neg              |                       | command line.                                                                                                  |  |  |

| 99     | D_CalPulse_pos            | LVDS output           | Channel D PACE Calibration Pulse                                                                               |  |  |

| 100    | D_CalPulse_neg            |                       | Injection command line.                                                                                        |  |  |

| 101    | ADC_CLK_pos               | LVDS output           | 40MHz ADC clock line.                                                                                          |  |  |

| 102    | ADC_CLK_neg               |                       |                                                                                                                |  |  |

|        | oit Optical Link interfa  | ce                    |                                                                                                                |  |  |

| 103    | TX_data<15>               | CMOS output           | Gigabit Optical Link data output.                                                                              |  |  |

| 104    | TX_data<14>               |                       |                                                                                                                |  |  |

| 105    | TX_data<13>               |                       |                                                                                                                |  |  |

| 106    | TX_data<12>               | 1                     |                                                                                                                |  |  |

| 107    | TX_data<11>               | 1                     |                                                                                                                |  |  |

| 108    | TX_data<10>               | 1                     |                                                                                                                |  |  |

| 109    | TX_data<9>                | 1                     |                                                                                                                |  |  |

| 110    | TX_data<8>                | 1                     |                                                                                                                |  |  |

| 111    | TX_data<7>                |                       |                                                                                                                |  |  |

| 112    | TX_data<6>                |                       |                                                                                                                |  |  |

| 113    | TX_data<5>                |                       |                                                                                                                |  |  |

| 114    | TX_data<4>                |                       |                                                                                                                |  |  |